Do you have a trouble to find 'how to write makefiles c'? You can find all the material on this web page.

Victimisation make and composition MakefilesUsing make. ...Creating a Makefile. ...Example simple Makefiles for a C (or C++)a slightly more generic simple makefileAn example of construction an executable from multiple .o files: # # This is an instance Makefile for letter a countwords program. ...Another makefile (using makedepend and more front make syntax)An instance simple Makefile for a Java. ...

Table of contents

- How to write makefiles c in 2021

- Makefile variables

- Makefile example c

- How to make a file on desktop

- Makefile for c program in linux

- How to make a new file

- Makefile example

- Makefile c

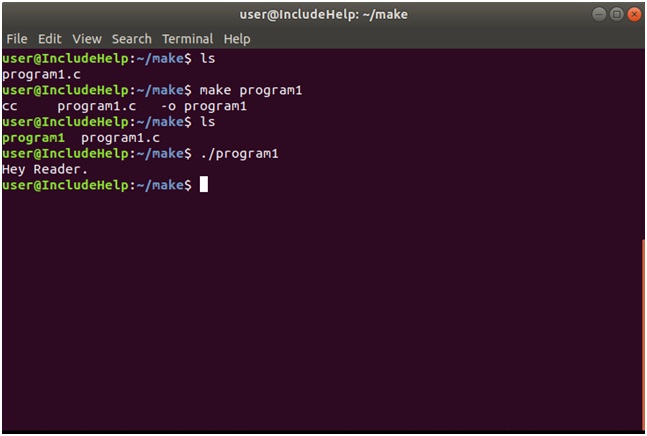

How to write makefiles c in 2021

This image shows how to write makefiles c.

This image shows how to write makefiles c.

Makefile variables

This picture shows Makefile variables.

This picture shows Makefile variables.

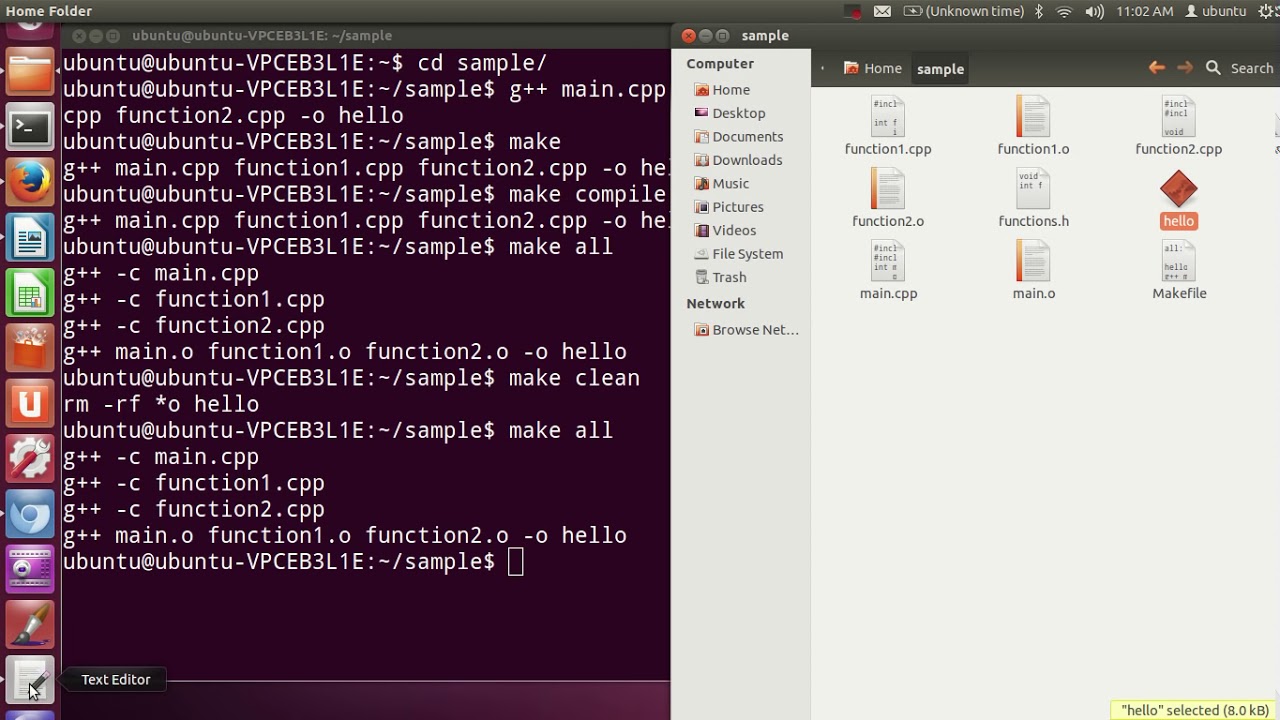

Makefile example c

This picture demonstrates Makefile example c.

This picture demonstrates Makefile example c.

How to make a file on desktop

This image shows How to make a file on desktop.

This image shows How to make a file on desktop.

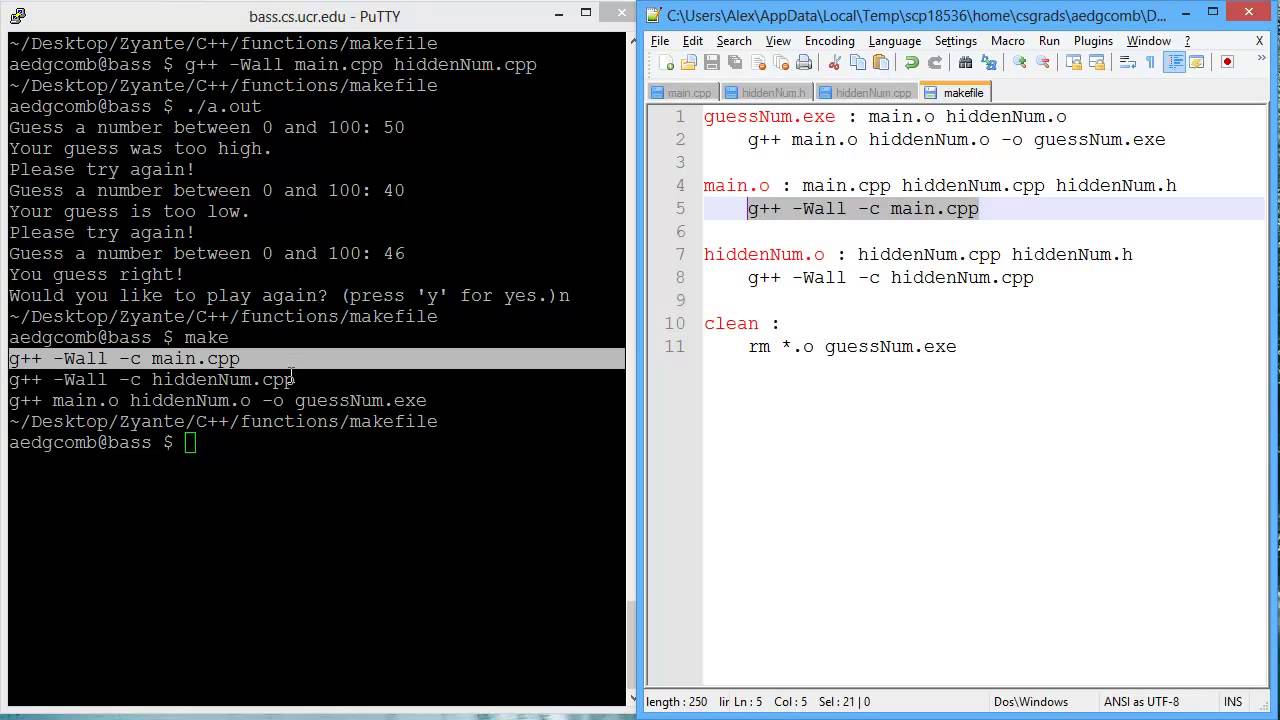

Makefile for c program in linux

This picture demonstrates Makefile for c program in linux.

This picture demonstrates Makefile for c program in linux.

How to make a new file

This image representes How to make a new file.

This image representes How to make a new file.

Makefile example

This picture illustrates Makefile example.

This picture illustrates Makefile example.

Makefile c

This picture shows Makefile c.

This picture shows Makefile c.

How does Makefile for C program compilation work?

Makefile with creating Object of source files and Cleaning Object files and Binary File. When we have multiple files then we can write command in Makefile to create Object files for each source file. If you do this – Only those files will be compiled which are modified.

What's the best way to write a make file?

GNU make Manual. A complete reference for writing makefiles from simple to advanced features. makedepend can be run on a Makefile (with a special line at the bottom) to autogerate compilation dependencies of files in a Makefile.

How to make a makefile on command line?

To use this makefile, simply cd to the directory and type “ makepp ”. Makepp will attempt to build the first target in the makefile, which is my_program. (If you don't want it to build the first target, then you have to supply a the name of the target you actually want to build on the command line.)

What do you need to know about makefile?

Makefile is a set of commands (similar to terminal commands) with variable names and targets to create object file and to remove them. In a single make file we can create multiple targets to compile and to remove object, binary files. You can compile your project (program) any number of times by using Makefile.

Last Update: Oct 2021

Leave a reply

Comments

Yer

22.10.2021 04:52Hullo guys, its ME again today i'm going to appearance you how to write a proficient makefile for A c++ project that you might have. Here is a selfsame minimal mingw hullo world program fashionable c.

Nohemy

20.10.2021 02:58Complete of our authorship experts have Associate in Nursing academic degree how to write brand files in one hundred and broad expertness in scholarly penning, which allows them to deliver brilliant essay help online. Iphone application programming delivered by stanford.

Marcis

22.10.2021 08:18Fifty-fifty though reading this article it was kinda hard for me to hold the actual proficiency behind the. The bedroc of the in advance method below were invented by.